关于电脑和功耗的话题

撰写于:2015年6月29日

作者:silex Wi-Fi专家

我想大家普遍都知道计算机是一种消耗电力来运行的“电子计算机”,但它并不是像电动机那样包含可动部件(虽然确实有冷却风扇和硬盘的旋转电机,但那里消耗的电力是微不足道的)。我认为很多人并不知道计算机为什么会消耗电力。这次我们就来聊聊这方面的话题。

什么是功率

功率是电压和电流的乘积。例如,如果电压是100V,电流是1A,那么消耗的功率就是100W。计算机的电源通常是固定电压(※注)的直流电,只有电流会根据负载状态变化,因此我们通常通过电源电压乘以消耗电流的平均值来计算消耗的功率。

(※注) 过去是5V,现在3.3V的越来越多,最近1.8V的也在增加。

那么,为什么计算机一运行就会有电流流动,这看似理所当然,实际上却是一个深奥的问题。这大致可以分为四种情况:(1)当电路构成具有电流性时,(2) 由于C-MOS电路特有的寄生电容和直通电流而产生时,(3) 由于泄漏电流而产生时,(4) 当电路构成具有电容性时。

(1) 电流性的电路构成

现代的数字计算机通过组合半导体开关元件——晶体管,构建二进制逻辑运算电路来实现计算(※注)。晶体管有两种类型:电流驱动的双极型晶体管和电压驱动的场效应晶体管(FET: Field Effect Transistor)。

(※注) 在很久以前的数字计算机中,也有使用电磁铁驱动开关的——继电器。提到旧时的计算机,很多人可能会想到“真空管”,但真空管主要用于模拟计算机,近似地将微分方程式解为电信号,与现代数字计算机的用途有所不同。

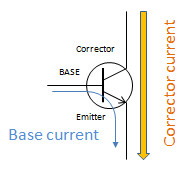

对于双极型晶体管,集电极和发射极之间的导电性受基极和发射极之间的电流控制。要使晶体管开启,电流必须流过基极。也就是说,只要使用双极型晶体管,降低功耗就总会有一个极限。

(上图)双极型晶体管的开关原理。通过基极到发射极之间流动的微小电流来控制集电极到发射极之间的电流。

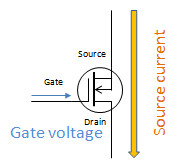

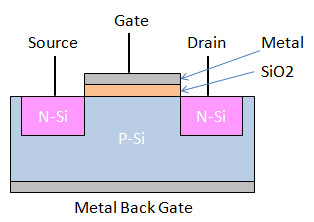

对于场效应晶体管(FET),源极和漏极之间的传导由栅极上的电压控制。FET栅极的电阻值(阻抗)非常高,特别是被称为MOS(金属氧化物半导体)类型的FET,因为输入栅极上有绝缘层,所以几乎没有电流流动。

(上图)MOS-FET的开关原理。源极和漏极之间的传导由施加到栅极的电压控制。

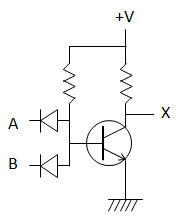

无论是双极型晶体管还是FET,根据如何组合晶体管来表示ON/OFF,电路的电流消耗也会有所不同。如果只使用一个晶体管的电路,在ON或OFF的任一状态下,电流都会通过电阻流动。在这种单通道电路中,仍然无法降低功耗。

(上图)DTL(二极管晶体管逻辑)NAND栅极。输入A、B的二极管作用于“流向”基极电流的方向,只要任一输入为Low,晶体管就会处于OFF状态,输出X就会通过电阻变为High。当A、B两个输入都为High时,基极电流流动,集电极电流通过输出级电阻“流向”到地,从而使输出变为Low。

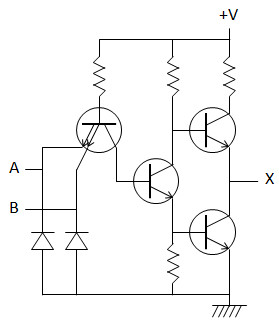

与此相对,当使用两个晶体管组合成交替切换的电路时,则无需为了丢弃电流而浪费电流。这种电路被称为图腾柱,由双极型晶体管组成的图腾柱电路称为TTL(晶体管-晶体管逻辑),由MOS FET组成的图腾柱电路称为C-MOS(互补型MOS)。C-MOS电路特别在省电性能上表现出色,除了在下文(2)和(3)所述的条件下,几乎不会有电流流动。

(上图)TTL NAND栅极。输出级的上下两个晶体管交替开启,因此不会像DTL那样浪费电流。另外,High侧输出不是通过电阻的泄流,而是由晶体管积极驱动,因此比DTL动作速度更快。输入级连接了一个具有多个发射极的晶体管,这是一种非常规连接方式,这是将晶体管作为二极管用,输入侧的动作原理与DTL相同。发射极下方的反向二极管是保护电路,没有逻辑上的意义。

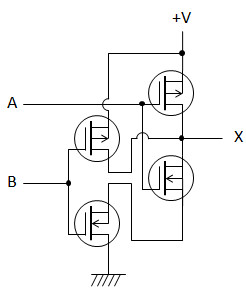

(上图)C-MOS NAND栅极。上下交替工作的C-MOS FET对,High侧并联,Low侧串联,当A、B两个输入都为High时,High侧FET关闭,Low侧FET开启,输出被驱动为Low level 。与双极型晶体管电路不同,请注意这里没有使用任何电阻。

早期的C-MOS存在动作速度慢和难以提高集成度的问题,因此在1970-1980年代,双极型的TTL和单边电阻的N-MOS逻辑占据了主流。然而,C-MOS技术的进步非常迅速,从90年代开始,越来越多的集成电路被 C-MOS 所取代。

(2) 寄生电容和直通电流

除非电路状态发生变化,否则 C-MOS 逻辑几乎不会产生任何电流。但在电路状态变化的瞬间,会有相对较大的电流短暂流动(这也被称为“峰值电流”)。

C-MOS 中的尖峰是由寄生电容和栅极上的直通电流造成的。寄生电容是指,在金属电极之间夹有绝缘层的 MOS-FET 结构本身就是一个电容器,因此在栅极部分会产生作为电容器的电容。直流电不能通过电容器,但交流电可以,所以在电压变化的瞬间,电流会流过栅极部分。

(图)MOS-FET的结构原理。乍一看,可以看出栅极和背栅极形成了电容器,但实际上栅极、源极和漏极之间存在各种寄生电容,栅极寄生电容就是这些寄生电容的组合。

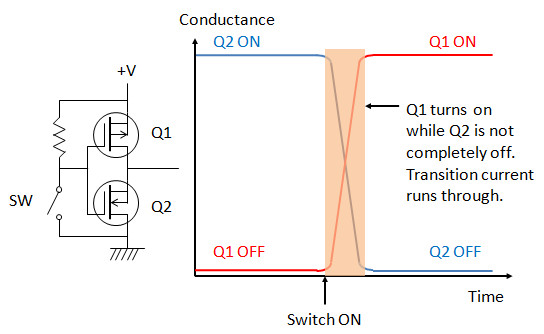

所谓的直通电流,是由于图腾柱电路中上下晶体管没有同时接通和断开时的延迟产生的。特别是在C-MOS中,只有上下晶体管中的一个“单独”处于ON状态的电路,但在切换的瞬间,会短暂出现“两者都ON”的状态,在这个瞬间,电流会流过上下晶体管。特别是C-MOS电路与TTL不同,输出端没有接入电阻,因此在某些情况下,可能会出现接近电源短路的状态。如果加入电阻,可以抑制直通电流,但这会构成与下一级栅极寄生电容之间的CR延迟电路,导致操作速度下降,这是一个令人头疼的问题。

(图)直通电流产生原理。Q1/Q2构成了C-MOS的逻辑反相器。当开关处于OFF状态时,Q2处于ON状态,输出为Low level;当开关切换到ON时,Q1变为ON状态,输出变为High Level。由于Q1和Q2在时间零点时状态不会立即切换,因此会存在两者同时处于ON状态的短暂时间,在这段时间内,电流会流过Q1和Q2。

由于寄生电容引起的消耗电流和直通电流都会随着工作频率的提高而增加,因此这成为了“提高计算机操作时钟频率会导致消耗电流增加”的主要原因。

(3) 漏电流

随着 LSI 越来越精细,工艺降到 90 纳米以下,这个问题变得越来越严重。电流和电压的载体——电子(不仅仅是电子,所有量子都适用)存在一种称为隧道效应的现象。根据海森堡的不确定性原理,量子的位置和速度只能以概率性的方式确定,反过来说,这意味着有一定概率量子可以突然“穿越”绝缘屏障,实际上这种现象确实会发生,电子因此移动并形成电流流出,这就是隧道效应。

个人电脑(PC)使用的CPU从90纳米工艺过渡到65纳米工艺大约是在2005年左右。在那个时期的CPU(如intel Pentium 4等)随着型号的更新换代,功耗趋向于增加,因其剧烈的发热现象被戏称为“硅加热器”、“煎蛋机”,其中一个原因就是由隧道效应引起的漏电流。摩尔定律(※注)也被认为可能走到了尽头,但后来发现使用高介电常数(High-K)绝缘材料如二氧化铪等可以抑制漏电流。

(※注) 这是基于英特尔公司的戈登·摩尔(Gordon Moore)在1965年发表的经验法则,即“半导体的集成度大约每1.5年翻一番”的预测。

用于传感器网络等的嵌入式SoC(※注)往往使用比个人电脑(PC)落后1到2代的工艺制造,而且只有在了解工艺的电流消耗特性后才进行商业化,原则上不会使用那些漏电流成为问题的“尚未成熟”的技术。

(※注) 系统级芯片(System on Chip)。将CPU、内存、输入输出电路等作为单个计算机系统所需的所有电路集成在一个硅芯片上。

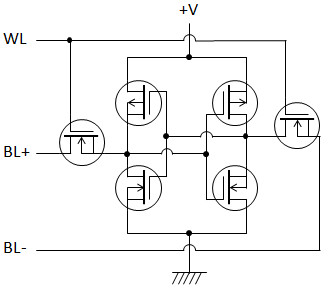

(4) 电容性电路构成

这主要是关于大容量内存DRAM(动态RAM)的应用。计算机内存有两种类型:静态内存(SRAM)和动态内存(DRAM)。SRAM通过组合晶体管,像触发器(※)一样在ON/OFF两种状态之间稳定,实现存储单元,一旦设置,信息可以保持到电源关闭。只有在重写存储器内容时才会消耗电流,如果只保留存储器,则几乎不消耗电流。

(※) “双稳态多谐振荡器”,通常称为“触发器”。

(图)C-MOS SRAM存储单元的原理电路。中间的四个FET构成了触发器,左右两侧的FET是存取栅极。WL是单元的存取信号(Active-High),BL+/BL-是读写共用的通用数据信号(+/-表示相反的位相)。当BL+/BL-处于输入状态时,通过断言WL可以读取当前状态,当BL+/BL-处于输出状态时,通过断言WL可以设置状态。

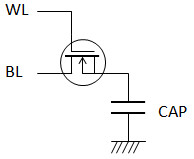

与此相反,DRAM是利用某种挥发性元件实现存储单元的,当设置完毕,信息就会随着时间的推移逐渐挥发。在信息完全挥发之前,需要读取信息并重新写入相同的信息,这个过程被称为“刷新”。DRAM的代表是电容性DRAM,它使用微小的电容器来保持信息。例如,将电容器充电的状态视为“1”,放电的状态视为“0”。

(图)DRAM存储单元的原理电路。只有一个电容器(CAP)和一个访问栅极FET。WL是单元访问信号(Active-High),BL是读写共用的数据信号。将BL设为Low并断言WL,电容器放电,从而在读取的同时写入 “0”。将BL设为High并断言WL,电容器充电,从而产生 “1 ”写入。

充电的电容器会因为内部电阻引起的泄漏电流而自动放电,因此每次刷新时都必须重新充电,这时会有电流流动。另外,读取DRAM时,是通过放电的方式释放电容器中储存的电荷(破坏性读取),所以读取后也必须重新充电,这时也会有电流流动。也就是说,DRAM即使只是存储信息也会消耗电流,而且在内存上读写信息时,流动的电流会越来越多。

之所以广泛使用这种不环保的DRAM,是因为它是目前实用化的存储元件中集成效率最高且读写速度最快的。对于需要以千兆字节为单位的高速内存的设备,如个人电脑,目前还没有其他实际的解决方案可以替代DRAM。

笔记本电脑通常都配备了“挂起”和“休眠”这两种待机模式,它们在保持DRAM上的信息方面有很大的不同。挂起模式是停止CPU的电源,但继续为DRAM提供保持信息所需的电力的待机模式(待机和恢复速度快,但在待机期间仍然持续消耗电池),而休眠模式是将DRAM中的所有信息保存到存储设备中,然后切断DRAM的电力的待机模式(待机和恢复时间较长,但在待机期间几乎不消耗电力,只消耗电池的内部放电)。

在传感器网络等用途中,通常只需要数十千字节,最多也就是兆字节单位的内存就足够了,因此可以使用不消耗电力的SRAM,而不是DRAM。最近,甚至可以在与CPU相同的硅芯片上集成大约1M字节的Flash-ROM和大约256K字节的SRAM,因此不再需要将内存连接用总线引出到外部引脚,只需将电源和时钟连接到大约8 平方毫米的64个引脚的封装上,就可以运行SoC。曾经梦想中的高功能、高性能与小型低价化的结合已经成为现实,但要充分利用这些特性并不是一件简单的事情。

努力进一步降低功耗

对于要求电池续航数月的嵌入式设备,如传感器网络,需要进行严格的低功耗设计。不仅要避免使用双极型逻辑和DRAM等浪费电流的元件,这还不够,因此采取了各种措施。

降低功耗的基本策略是“只在需要时启动电路,其他时候尽量停止”。这其中理由如第(2)段所述,C-MOS逻辑具有一旦启动就会消耗更多电流的特性。对于“尽量”的解释不同,会有不同的实现方式,大致可以分为四个阶段:(1) 降低操作时钟,(2) 降低供电电压,(3) 停止时钟供应,(4) 停止电源供应。

现代的嵌入式SoC能够对内部电路的功能分别进行电源和时钟管理,可以精细控制电路中哪些部分的电源或时钟应该降低或停止,以及降低到什么程度。例如,在等待串行端口接收数据时,可以只保持串行接收电路的时钟运行,而将CPU核心的时钟停止并降低供电电压,对于不使用的外围电路可以停止其时钟或电源供应。这样的操作已经成为可能。

这样的SoC作为高性能的代价,其寄存器的数量变得非常庞大,仅通过阅读手册很难立即理解应该按照什么顺序初始化才能使设备工作。为了快速开发高性能 SoC 并将其商业化,会考验到实时操作系统(RTOS)、设备驱动程序、示例程序和评估套件(EVK)等芯片制造商的软件支持能力。过去,芯片制造商的官方手册几乎是“不友好”的代名词,充满了难以理解的晦涩表述(※注),但不管硅芯片多么优秀,如果支持服务做得不好,产品也难以销售。制造商的官方手册也已经有了很大的改进,这对我们工程师来说是个好消息。

(※注) 指的是Intel 8259A中断控制器的特殊完全多重模式(Special Fully Nested Mode)的解释,这是一个曾经让人多次阅读后仍然感到困惑的问题。原文也不是易于理解的,而日文翻译版本尤其糟糕,导致意思不明确。

总结

本期,我们离开了 “无线 ”的框架,将功耗产生的原理和低功耗方法作为微型计算机的一般理论进行了阐述。降低功耗不仅作为节能的一般理论是有效的,而且对于移动信息设备和在无人时仍能继续默默工作的传感器网络来说,低功耗也是不可或缺的技术。

直到90年代中期左右,以电池为动力的微计算机系统还属于比较特殊的类别,即使有必要使用,也是使用NiCd或NiMH等大容量的可充电电池。然而,在过去的大约10年里,使用干电池或纽扣电池等小容量一次性电池的系统数量有所增加,并且从外界获取电力运行的能源收集(Energy Harvest)技术,如太阳能电池和热电电池,也在被积极研究。虽然我不喜欢追逐“移动”、“可穿戴”、“互联网”、“IoT”等流行词,但我认为人与信息的关系确实在变化。在这样的时代背景下,未来低功耗技术将变得越来越重要。

相关文章

Silex 产品信息

我们的技术和产品旨在建立设备之间的通信,并确保这种通信能够顺畅地稳定进行。而且,更重要的是,使用 Silex 技术和产品的客户可以绝对放心。 我们正是致力于实现这一目标。